# **Solutions - Final Exam**

(December 9th @ 7:00 pm)

Clarity is very important! Show your procedure!

# **PROBLEM 1 (15 PTS)**

- Determine whether the following statements are True or False. If the statement is False, explain why.

- ✓ HCS12D SCI1: With E-clock = 24 MHz, it is possible for the frequency of the receiver clock to be 2560 Hz. FALSE.  $Min. Rx \ clock = \frac{24 \times 10^6}{SBR} = \frac{24 \times 10^6}{2^{13} - 1} = 2930.0451 \ Hz$ . Since 2560 < 2930.0451 Hz, SBR requires more than 13 bits.

- ✓ CAN: The Bit Rate of System A is identical to that of System B. The CAN Bit Time of System A is 8 time quanta, and the CAN Bit Time of System B is 10 time quanta. Thus, the CAN Bit Time (in units of time) of System A is different to that of System B.

**FALSE**. If the Bit Rate of two systems is the same, the CAN Bit Time (in units of time) is the same:  $\frac{1}{Rit\ Rate}$

- ✓ The Real-Time Interrupt can be disabled by setting bit I of CCR to `1'.

TRUE

- ✓ HCS12D CAN: Hard Synchronization takes place at the beginning of the frame, when the start of frame bit changes the state of the bus from dominant (0) to recessive (1).

FALSE. The start of frame bit changes the state of the bus from recessive (1) to dominant (0).

- ✓ /XIRQ Interrupt: A user can always disable it at any time during program execution by setting bit X of CCR to `1'. FALSE. Once the /XIRQ is enabled, the user program cannot disable it.

- ✓ HCS12D SCI1: The receiver clock is 16 times faster than the transmitter clock to allow for synchronization. TRUE

- Complete:

- √ HCS12D ATD0, V<sub>DD</sub> = 5v: The minimum number of bits that makes sure that the average quantization error never exceeds 0.001v is 12.

Average Quantization error: This is the voltage of 1/2 LSB:  $\frac{1}{2^{n+1}} \times 5 < 0.001v \rightarrow 2^{n+1} > 5000 \rightarrow n+1 > 12.2877$   $\Rightarrow$  Minimum  $\mathbf{n} = \mathbf{12}$ .

- ✓ HCS12D Timer with E-clock= 24 MHz and pre-scale factor 8: A count from 0 to the maximum count lasts <u>21.8453</u> ms  $Timer\ Clock = \frac{24}{8} = 3MHz \rightarrow Timer\ Clock\ Period = \frac{1}{3}us$ . A 0 to  $2^{16} 1$  count takes:  $\frac{1}{3} \times 2^{16}us = \frac{65536}{3}us = 21.8453ms$ .

- ✓ HCS12D SPI0: If E-clock = 24 MHz and SPI0BR = 0x57, the Baud Rate is \_\_\_\_\_\_ Hz.  $Baud\ Rate\ Divisor = (SPPR + 1) \times 2^{(SPR+1)} = (5+1) \times 2^{(7+1)} = 1536 \rightarrow Baud\ Rate = \frac{24MHz}{1536} = 15625Hz$

- Miscellaneous questions:

- ✓ PWM signal generation: Mention one advantage of using the PWM Module instead of the Output Compare function? A PWM signal generated with the Output Compare function either requires continuous attention by the processor or requires an Interrupt. The PWM requires neither, and allows for more efficient coding.

- CAN: What is bit stuffing?

It is a procedure applied by the Transmitter: every 5 consecutive identical bits, a complemented bit is included.

- ✓ HCS12 Timer: Briefly describe the Input Capture function.

Whenever an event is present on an Input Capture pin, the value of the Timer Counter (TCNT) is loaded on the respective Input Capture Register.

- ✓ When servicing an Interrupt, the HCS12 stores PC and CPU registers in the Stack. What information does the PC register contain?

- The PC (Program Counter) contains the Return Address, i.e., the address of the instruction immediately following the instruction at which the Interrupt was issued.

Mark the correct option:

✓ At power-on, the /IRQ Interrupt is:

<u>Disabled</u>

Enabled

✓ HCS12D: Which of these two can be modified by the user?

**Interrupt Vector**

Vector Address

## **PROBLEM 2 (10 PTS)**

■ HCS12D - SCI1: Complete the table. E-clock = 24 MHz.

| <b>Baud Rate = Tx clock frequency</b> (Hz) | Rx clock frequency (Hz) | SCI1BDH | SCI1BDL |

|--------------------------------------------|-------------------------|---------|---------|

| 2000                                       | 32000                   | 02      | EE      |

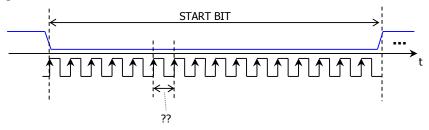

The figure below depicts the process of detection of a Start Bit. Using the parameters above, determine the period of the clock signal in the figure below.

$$Tx \ clock = \frac{24 \times 10^6}{16 \times SBR} = 2000 \rightarrow SBR = 750 = 0x02EE$$

$Rx \ clock = 2000 \times 16 = 32000 \ Hz$

The clock signal is the Receiver clock. Thus, its period is  $\frac{1}{32000} = 31.25us$

# **PROBLEM 3 (20 PTS)**

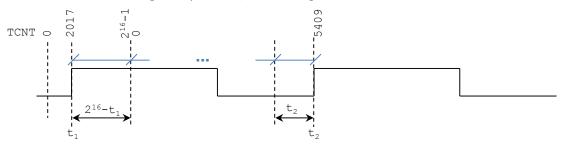

• (10 pts) HCS12D Timer: A program measures the period of a signal by using the Input Capture function and reading the TCNT values of two consecutive edges. In particular, the following values were read: 2017 and 5409.

✓ What is the frequency of the signal? E-clock = 24 MHz, Timer Pre-scale Factor = 4.

Timer Clock =

$$\frac{24}{4}$$

= 6MHz  $\rightarrow$  Timer Clock Period =  $\frac{1}{6}$  us

$$\rightarrow Signal\ Period = (2^{16} - t_1 + (ovcnt - 1) \times 2^{16} + t_2) \times \frac{1}{6}us = (2^{16} - 2017 + 2 \times 2^{16} + 5409) \times \frac{1}{6}us = \frac{100}{3}ms$$

$\rightarrow$  Signal Frequency =  $\frac{3}{100}$  KHz = 30Hz

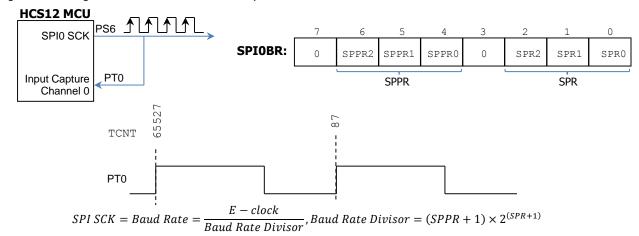

(10 pts) HCS12D Timer and SPI Unit: We want to measure the clock frequency of the SPI unit with the Timer. To this end, we wire the SPI Clock (SCK) to an Input Capture Channel. We measure the SCLK period by detecting 2 consecutive rising edges and storing the Timer counter values. They are 65527 and 87.

- ✓ What are the minimum and maximum attainable periods (in units of time) for the SPI clock?

- ✓ What is the Baud Rate (and the value of SPIOBR) of the SPI Unit? Hint: Consider the range of possible SPI clock periods to determine the number of times the Timer Counter rolls from \$FFFFF to \$0000. E-clock = 24 MHz. Timer Pre-scale Factor = 2.

SPI Clock Min. Frequency requires SPI0BR=01110111  $\rightarrow$ :  $\frac{24}{8\times2^8}MHz = 11.71875KHz \rightarrow$  SCK Max. Period:  $\frac{256}{3}us = 85.33us$

SPI Clock Max. Frequency requires SPI0BR=000000000  $\rightarrow$ :  $\frac{24}{2}MHz = 12 MHz \rightarrow$  SCK Min. Period:  $\frac{1}{12}us$

Timer Clock =  $\frac{24}{2}$  = 12MHz  $\rightarrow$  Timer Clock Period =  $\frac{1}{12}$ us

A count from 0 to  $2^{16}$ -1 would take:  $\frac{1}{12} \times 2^{16} us = \frac{16384}{3} us$ . The max. period of SCK is far lower than this.  $85.33us \ll \frac{16384}{3} us$   $\Rightarrow$  The Timer has only rolled once from \$FFFFF to \$0000 between the captured values of 65527 and 87.

→ SCK Period =  $(2^{16} - t_1 + (ovcnt - 1) \times 2^{16} + t_2) \times \frac{1}{12}us = (2^{16} - 65527 + 87) \times \frac{1}{12}us = 8us$ → SCK Frequency =  $125 \, \text{KHz} \rightarrow 125 \, \text{KHz} = \frac{24 \, \text{MHz}}{Baud \, Rate \, Divisor}$ , Baud Rate Divisor =  $192 = (SPPR + 1) \times 2^{(SPR + 1)}$

$\rightarrow$  SPPR = 2, SPR = 5 (there can be more than one solution)

→ SPI0BR = 00100101

# PROBLEM 4 (20 PTS)

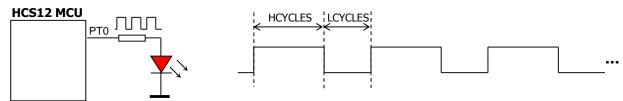

- Assuming that brightness is proportional to the duty cycle of a square waveform, a PWM signal can control the brightness of an LED. We want to dim the LED brightness in the following manner:

- 1 second at 95% intensity, 1 second at 60% intensity, 1 second at 45% intensity, 1 second at 30% intensity, and 1 second at 4% intensity

- We use the Timer Output Compare Channel 0 to generate 80Hz square waveforms with different duty cycles. The code requires us to specify HCYCLES and LCYCLES (in number of Timer cycles).

✓ Complete the following table, where the Timer Pre-scale factor must be maximized for each case. E-clock = 24 MHz.

3 Instructor: Daniel Llamocca

| <b>Duty Cycle</b> | HCYCLES | LCYCLES | Pre-scale Factor | Timer Clock<br>Frequency |

|-------------------|---------|---------|------------------|--------------------------|

| 95%               | 35625   | 1875    | 8                | 3 MHz                    |

| 60%               | 5625    | 3750    | 32               | 750 KHz                  |

| 45%               | 16875   | 20625   | 8                | 3 MHz                    |

| 30%               | 5625    | 13125   | 16               | 1.5 MHz                  |

| 4%                | 375     | 9000    | 32               | 750 KHz                  |

80 Hz square waveform has a period of  $\frac{1}{80} = 12.5ms$   $TCYCLES \times \frac{PF}{24 \times 10^6} = 12.5 \times 10^{-3}, \ TCYCLES = HCYCLES + LCYCLES, \ PF: \ Pre-scale factor (1,2,4,8,16,32,64,128)$   $TCYCLES \times \frac{PF}{24} = 12500 \rightarrow TCYCLES = \frac{300000}{PF} \rightarrow HCYCLES = \frac{300000}{PF} \times (Duty\ Cycle)$   $- \ DC = 95\%: \ HCYCLES = \frac{300000}{PF} \times 0.95 \ \text{must be an integer lower or equal than 65535}. \ The \ maximum\ PF \ that allows \ this \ is \ 8. \ Thus \ HCYCLES = 35625, \ LCYCLES = 1875.$   $- \ DC = 60\%: \ HCYCLES = \frac{300000}{PF} \times 0.6 \ \text{must be an integer lower or equal than 65535}. \ The \ maximum\ PF \ that allows \ this \ is \ 32. \ Thus \ HCYCLES = 5625, \ LCYCLES = 3750.$

- 32. Thus HCYCLES = 5625, LCYCLES = 3750.

- DC = 45%:  $\frac{300000}{FF} \times 0.45$  must be an integer lower or equal than 65535. The maximum PF that allows this is 8. Thus  $\frac{HCYCLES}{F} = \frac{300000}{10000} \times 0.45$  must be an integer lower or equal than 65535. The maximum PF that allows this is 8. Thus  $\frac{HCYCLES}{F} = \frac{300000}{100000} \times 0.45$  must be an integer lower or equal than 65535. The maximum PF that allows this

- DC = 30%:  $\frac{300000}{PF} \times 0.3$  must be an integer lower or equal than 65535. The maximum PF that allows this is 16. Thus HCYCLES = 5625, LCYCLES = 13125.

- DC = 4%:  $HCYCLES = \frac{300000}{PF} \times 0.04$  must be an integer lower or equal than 65535. The maximum PF that allows this is 32. Thus HCYCLES = 375, LCYCLES = 9000.

# PROBLEM 5 (15 PTS)

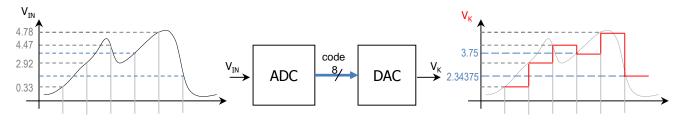

Analog to Digital Conversion: The figure depicts the process of converting 6 consecutive analog values. Using the successive approximation algorithm (when needed) and/or the formula for quantized voltage, complete the table below. VDD=5v.

Formula for Quantized voltage:  $V_k = \left(\frac{k}{2^n}\right) V_{DD}$

| V <sub>IN</sub> (v) | 8-bit code | $V_k(\boldsymbol{v})$ |

|---------------------|------------|-----------------------|

| 0.33                | 00010000   | 0.3125                |

| 2.92                | 10010101   | 2.91015625            |

| 4.47                | 11100100   | 4.453125              |

| 3.76                | 11000000   | 3.75                  |

| 4.78                | 11110100   | 4.765625              |

| 2.35                | 01111000   | 2.34375               |

V<sub>IN</sub> = 0.33v, 8-bit code: 00010000:

$$00001000_2 = 120$$

$$\rightarrow V_k = \left(\frac{120}{2^8}\right) 5 = 0.3125$$

#### $V_{IN} = 2.92v$ :

$$b_7 = 1 \rightarrow Code = 10000000 \rightarrow k = 128 \rightarrow V_k = \left(\frac{128}{2^8}\right) 5 = 2.5v \leq Vin \rightarrow b_7 = 1$$

$$b_6 = 1 \rightarrow Code = 11000000 \rightarrow k = 192 \rightarrow V_k = \left(\frac{192}{2^8}\right) 5 = 3.75v > Vin \rightarrow b_6 = 0$$

$$b_5 = 1 \rightarrow Code = 10100000 \rightarrow k = 160 \rightarrow V_k = \left(\frac{160}{2^8}\right) 5 = 3.125v > Vin \rightarrow b_5 = 0$$

$$b_4 = 1 \rightarrow Code = 10010000 \rightarrow k = 144 \rightarrow V_k = \left(\frac{144}{2^8}\right) 5 = 2.8125v \leq Vin \rightarrow b_4 = 1$$

$$b_3 = 1 \rightarrow Code = 10011000 \rightarrow k = 152 \rightarrow V_k = \left(\frac{152}{2^8}\right) 5 = 2.96875v > Vin \rightarrow b_3 = 0$$

$$b_2 = 1 \rightarrow Code = 10010100 \rightarrow k = 148 \rightarrow V_k = \left(\frac{148}{2^8}\right) 5 = 2.890625v \leq Vin \rightarrow b_2 = 1$$

$$b_1 = 1 \rightarrow Code = 10010110 \rightarrow k = 150 \rightarrow V_k = \left(\frac{150}{2^8}\right) 5 = 2.9296875v > Vin \rightarrow b_1 = 0$$

$$b_0 = 1 \rightarrow Code = 10010101 \rightarrow k = 149 \rightarrow V_k = \left(\frac{149}{2^8}\right) 5 = 2.91015625v \leq Vin \rightarrow b_0 = 1$$

$$\Rightarrow Code = 10010101, V_k = \left(\frac{149}{2^8}\right) 5 = 2.91015625v$$

#### $V_{IN} = 4.47v$ , 8-bit code: 11100100:

$$11100100_2 = 228$$

$$\rightarrow V_k = \left(\frac{228}{2^8}\right) 5 = 4.453125$$

**V<sub>IN</sub> = 3.76v,**

$$V_k = 3.75v$$

$\rightarrow V_k = \left(\frac{k}{2^8}\right)5 = 3.75v \rightarrow k = 192 \rightarrow 8$ -bit code: 11000000

## $V_{IN} = 4.78v$ :

$$b_7 = 1 \rightarrow Code = 10000000 \rightarrow k = 128 \rightarrow V_k = \left(\frac{128}{2^8}\right) 5 = 2.5v \leq Vin \rightarrow b_7 = 1$$

$$b_6 = 1 \rightarrow Code = 11000000 \rightarrow k = 192 \rightarrow V_k = \left(\frac{192}{2^8}\right) 5 = 3.75v \leq Vin \rightarrow b_6 = 1$$

$$b_5 = 1 \rightarrow Code = 11100000 \rightarrow k = 224 \rightarrow V_k = \left(\frac{224}{2^8}\right) 5 = 4.375v \leq Vin \rightarrow b_5 = 1$$

$$b_4 = 1 \rightarrow Code = 11110000 \rightarrow k = 240 \rightarrow V_k = \left(\frac{240}{2^8}\right) 5 = 4.6875v \leq Vin \rightarrow b_4 = 1$$

$$b_3 = 1 \rightarrow Code = 11111000 \rightarrow k = 248 \rightarrow V_k = \left(\frac{248}{2^8}\right) 5 = 4.84375v > Vin \rightarrow b_3 = 0$$

$$b_2 = 1 \rightarrow Code = 11110100 \rightarrow k = 244 \rightarrow V_k = \left(\frac{244}{2^8}\right) 5 = 4.765625v \leq Vin \rightarrow b_2 = 1$$

$$b_1 = 1 \rightarrow Code = 11110110 \rightarrow k = 246 \rightarrow V_k = \left(\frac{246}{2^8}\right) 5 = 4.8046875v > Vin \rightarrow b_1 = 0$$

$$b_0 = 1 \rightarrow Code = 11110101 \rightarrow k = 245 \rightarrow V_k = \left(\frac{245}{2^8}\right) 5 = 4.78515625v > Vin \rightarrow b_0 = 0$$

$$\Rightarrow Code = 11110100, V_k = \left(\frac{244}{2^8}\right) 5 = 4.765625v$$

$$V_{IN} = 2.35v$$

,  $V_k = 2.34375v$

$\rightarrow V_k = {k \choose 28} 5 = 2.34375v \rightarrow k = 120 \rightarrow 8$ -bit code: 01111000

### PROBLEM 6 (20 PTS)

A CAN system has the following characteristics:

- Bit rate = 500 kbps Bus length = 100 m

- Bus propagation delay =  $4 \times 10^{-9} \, \text{S}/m$

- Transmitter (MCP2551 Transceiver) plus receiver propagation delay = 150 ns at 85 °C

- HCS12 CAN Module: E-clock = 24 MHz, Oscillator clock = 8 MHz. Pre-scale factor = CANnBTR0 (5..0). The CAN clock source is selected by CANnCTL1(6).

- Calculate: i) CAN Pre-scale factor, ii) Time Quantum, iii) CAN Bit Time (in units of time and in time quanta), and iv) Time segments (in time quanta) for the following cases:

| sync_seg prop_seg phase_seg1 phase_seg2 | į |          |          |            |            |

|-----------------------------------------|---|----------|----------|------------|------------|

|                                         |   | sync_seg | prop_seg | phase_seg1 | phase_seg2 |

- ✓ CANnCTL1(6) = 0. Clock Source: Oscillator Clock

- ✓ CANnCTL1(6) = 1. Clock Source: E-clock

5 Instructor: Daniel Llamocca

## Clock Source: E-clock: 24 MHz

- CAN Bit Time =  $t_{NBT} = \frac{1}{500 \ kbps} = 2us$  Bus delay =  $100m \times (4 \times 10^{-9} \ S/m) = 400ns \rightarrow t_{PROP\_SEG} = 2 \times (400 + 150) = 1100ns$  Pre-scaler: let's pick M = 4:  $t_Q = 4 \times \frac{1}{24MHz} = \frac{1}{6} us$ . Then: CAN Bit Time =  $NBT = \frac{2us}{\frac{1}{6}us} = 12$

$$\rightarrow prop\_seg = \left\lceil \frac{t_{PROP\_SEG}}{t_Q} \right\rceil = \left\lceil \frac{1100ns}{\frac{1}{6}us} \right\rceil = 7. \rightarrow sync\_seg + prop\_seg + phase\_seg1 + phase\_seg2 = NBT = 12$$

- $\rightarrow$  phase\_seg1 + phase\_seg2 = 12 7 1 = 4

- $\rightarrow phase\_seg2 = phase\_seg2 = 2$

- In summary: M = 4, NBT = 12,  $sync\_seg = 1$ ,  $prop\_seg 1 = 7$ ,  $phase\_seg 1 = 2$ ,  $phase\_seg 2 = 2$

#### **Clock Source: Oscillator Clock: 8 MHz**

- $\begin{array}{l} \ \ \, \textit{CAN Bit Time} = t_{NBT} = \frac{1}{500 \ kbps} = 2us \\ \ \ \, \textit{Bus delay} = 100m \times (4 \times 10^{-9} \ \text{S/}_{m}) = 400ns \rightarrow t_{PROP\_SEG} = 2 \times (400 + 150) = 1100ns \\ \ \ \, \text{Pre-scaler: let's pick } M = 1: \ t_{Q} = 1 \times \frac{1}{8MHz} = \frac{1}{8} \ us. \ \text{Then: } \ \textit{CAN Bit Time} = NBT = \frac{2us}{\frac{1}{8}us} = 16 \end{array}$

$$\rightarrow prop\_seg = \left\lceil \frac{t_{PROP\_SEG}}{t_Q} \right\rceil = \left\lceil \frac{1100ns}{\frac{1}{8}us} \right\rceil = 9. \rightarrow sync\_seg + prop\_seg + phase\_seg1 + phase\_seg2 = NBT = 16$$

- $\rightarrow$  phase\_seg1 + phase\_seg2 = 16 9 1 = 6.

- $\rightarrow phase\_seg2 = phase\_seg2 = 3$

- In summary: M = 1, NBT = 16,  $sync\_seg = 1$ ,  $prop\_seg = 9$ ,  $phase\_seg = 3$ ,  $phase\_seg = 3$

- Note that  $prop\_seg1 \le 8$ . In general, this means that we cannot use 8 MHz. A workaround would be to add 1 to phase\_seg1 (since this segment can only grow to compensate for delays in the bit edge), though this is a bit outside the scope of the material.

6